# Single-Step Formation of $ZnO/ZnWO_x$ Bilayer Structure via Interfacial Engineering for High Performance and Low Energy Consumption Resistive Memory with Controllable High Resistance States

Shih-Ming Lin, Jian-Shiou Huang, Wen-Chih Chang, Te-Chien Hou, Hsin-Wei Huang, Chi-Hsin Huang, Su-Jien Lin, and Yu-Lun Chueh\*

Department of Materials Science and Engineering, Center For Nanotechnology, Material Science, and Microsystem, National Tsing Hua University, Hsinchu, Taiwan, ROC

Supporting Information

**ABSTRACT:** A spontaneously formed  $ZnO/ZnWO_x$  bilayer resistive memory via an interfacial engineering by one-step sputtering process with controllable high resistance states was demonstrated. The detailed formation mechanism and microstructure of the  $ZnWO_x$  layer was explored by X-ray photoemission spectroscopy (XPS) and transmission electron microscope in detail. The reduced trapping depths from 0.46 to 0.29 eV were found after formation of  $ZnWO_x$  layer, resulting in an asymmetric I-V behavior. In particular, the reduction of compliance current significantly reduces the switching current to reach the stable operation of device,

enabling less energy consumption. Furthermore, we demonstrated an excellent performance of the complementary resistive switching (CRS) based on the  $ZnO/ZnWO_x$  bilayer structure with DC endurance >200 cycles for a possible application in three-dimensional multilayer stacking.

KEYWORDS: resistive switching memory, ZnWO, interface engineering, ZnO, complementary resistive switching (CRS), sneak path

# 1. INTRODUCTION

Development of resistive random access memory (ReRAM) is one of mainstreams for next generation nonvolatile memories (NVM) because of its fast switching speed, low power consumption, excellent endurance, and easy integration with current devices. 1-5 A two terminal stacking configuration is generally considered as the best structure to reach a highly stacking density of ReRAM devices via three-dimensional (3D) crossbar process, which can geometrically achieve highest packing density with a maximum stacking size of  $4F^2$  (F =minimum feature size).<sup>6</sup> Sneak path, an inherent disadvantage, is typically resulted from the current flowing through the neighboring devices while employing two terminals stacking together for the 3D crossbar application. To avoid the sneak path, a connection with other passive devices, such as rectifying diode (1D1R), switching transistor (1T1R), and threshold selector (1S1R) as the switching elements is a simple way to prevent the whole system from the influence of the bypass current as the device is operated at a low resistive state, whereas the incorporation of passive devices would make fabrication process much complicated.7-12

A demonstration of connecting two bipolar ReRAM cells using solid electrolytes as switching materials has been reported to solve the sneak paths, but the overall processes are relatively complicated.<sup>2,13</sup> Therefore, the material choice with a simple fabrication process is an important consideration. Metal oxides,

such as HfO<sub>2</sub>, 4 WO<sub>3</sub>, 14 TiO<sub>2</sub>, 15 ZnO, 16,17 and NiO, 18 are promising materials for ReRAM applications because of their controllable compositions with an easy sputtering process at low temperature. Among these metal oxide materials, zinc oxide (ZnO) has many superior characteristics in optics and electronics, such as a wide and direct band gap of ~3.37 eV, adjustable electrical properties via the doping of different dopants, and much lower synthetic temperature. 19 ZnO-based thin film ReRAM devices were found to have a promising resistive switching behavior with either unipolar or bipolar resistive switching characteristics. a The preferred c-axis orientation of the ZnO film enables a high power consumption due to high reset current of 20-40 mA and leakage current along grain boundaries, which results in unstable operation and is a challenge in developing the ZnO-based RRAM. 16,17 Some literature reported that the increase in the resistance in high resistance state could be achieved by controlling dopants, such as Ni and Li.<sup>20,21</sup> Formation of interfacial metal oxide on resistive switching metal oxide layer, namely bilayer structure, after capping a reactive metal as electrode can usually act as the oxygen reservoir, providing sufficient oxygen vacancies to improve switching uniformity and reliability. However, a simple

Received: May 6, 2013 Accepted: July 22, 2013 Published: July 22, 2013 and direct way of single-step formation of bilayer structure in order to reduce to fabrication process and process cost is essential.<sup>4</sup>

In this regard, we demonstrated a spontaneous formation of  $\rm ZnO/ZnWO_x$  bilayer structure via interface engineering by one-step sputtering process for the ReRAM application. The advantages of the spontaneously formed  $\rm ZnWO_x$  layer beneath the ZnO layer can increase the high resistance value of devices but also reduce the compliance current of maintaining a stable operation of devices, enabling less power consumption. The detailed formation mechanism of  $\rm ZnWO_x$  layer during the sputtering process was explored by X-ray photoemission spectroscopy (XPS) measurements. Furthermore, the complementary resistive switching (CRS) based on the  $\rm ZnO/ZnWO_x$  bilayer structure via antiserial stacking to avoid the sneak path was demonstrated with DC endurance >200 cycles for a possible application in three-dimensional multilayer stacking.

# 2. EXPERIMENTAL SECTION

**Fabrication of Devices.** RF-magnetron sputtering system was used to prepare Pt/ZnO/Pt and Pt/ZnO/ZnWO<sub>x</sub>/W devices. The bottom W/Pt electrode was deposited with W thickness of 7, 15, and 30 nm on the Ti/SiO<sub>2</sub>/Si (100) substrate. Subsequently, 30 nm thick ZnO film was deposited upon the W layer at room temperature with a power density of 2 W/cm² and a working pressure of 5 × 10<sup>-3</sup> Torr, respectively. During sputtering process, the ZnWO<sub>x</sub> layer could be formed simultaneously. Pt top electrodes were patterned on ZnO films by a shadow mask with the diameter of 200, 100, and 50 μm.

**Characterization.** Keithley 4200 semiconductor parameter analyzer under DC sweeping mode was used to measure I-V characteristics of devices. During voltage sweeping mode, the positive bias was defined as the current flowed from Pt top to W bottom electrode grounded. The nanostructure of the Pt/ZnO/ZnWO<sub>x</sub>/W was examined by field-emission transmission electron microscopy (FE-TEM, JEM-3000F, JEOL operated at 300 kV with point-to-point resolution of 0.17 nm) and atomic composition was analyzed by electron dispersive spectrometer (EDS). Meanwhile, the depth profile and the interfacial bonding state of different stacks were examined by X-ray photoelectron spectroscopy, which were calibrated by Pt bottom electrode (XPS, Perkin-Elmer Phi 1600 ESCA system, operated at 25 mA/15 kV). The etching rate, beam current density, and accelerating voltage of argon plasma were 0.12 nm/s (3.5 nm in 30 s), and 2.8 ×  $10^3$  A/m² (25 mA in 9 mm²), and 15 keV, respectively.

# 3. RESULTS AND DISCUSSION

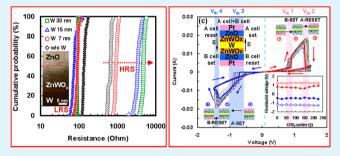

A ZnO film as a resistive switching layer switched by top platinum (Pt) and bottom tungsten (W) metal layers as the contact electrodes was prepared by a sputtering process. A very thin layer, namely, ZnWO<sub>x</sub> layer could be simultaneously formed as a mediated layer under the ZnO layer while the sputtering ZnO layer was being formed on the W electrode layer. The Pt/ZnO/ZnWOx/W bilayer structure is schematically illustrated in inset of Figure 1(a, where the different thicknesses of W layers on Pt electrodes from 7 to 30 nm were prepared. The corresponding current-to-voltage (I-V) switching loops for the ZnO/ZnWO<sub>x</sub> bilayer and a pure ZnO layer were measured for comparison as shown in Figure 1a, respectively. Basically, "SET" process is defined as a sudden increasing of current owing to a switching of the resistive state from high resistance state (HRS) to low resistance state (LRS) after a SET bias was applied with compliance current of 10 mA while "RESET" process, which is opposite to the "SET" process, exhibits a sudden decreasing of current due to the resistance switching from the LRS to the HRS after a RESET bias was applied. The switching mechanism is called bipolar

**Figure 1.** (a) Typical I-V behaviors of with and without formation of  $ZnO/ZnWO_x$  bilayer structures with different as-grown W layer thicknesses. Inset shows the configuration of devices. (b) Cumulative probabilities of LRS and HRS for Pt/ZnO/Pt and  $Pt/ZnO/ZnWO_x/Pt$  devices with different as-grown W layer thicknesses.

switching. For all devices at the HRS, the slopes of I-V curves were distinctly found to be decreased with increasing of asgrown W layer thicknesses, revealing the increasing of device resistance owing to the increasing of the  ${\rm ZnWO_x}$  layer thickness formed from the as-grown W layer after sputtering process of ZnO layer (Figure 1a). Figure 1b shows the cumulative probability as the function of resistance with different thicknesses of as-grown W layers from 7 to 30 nm with read voltage of 0.1 V, respectively. The HRS increases with the increasing of as-grown W layer thicknesses, resulting in the enhanced HRS/LRS ratio of up to ~300%, whereas saturation could be obtained as the thickness of the as-grown W layer over ~15 nm.

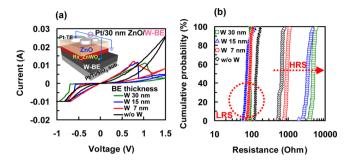

To confirm the phase and structure of ZnWO, layer, grazing incidence X-ray diffraction (GIXRD) was used to analyze crystal structure of layers by changing different incident angles from 0.3 ° to 0.5°, for which the structure information from top ZnO to bottom ZnWO<sub>x</sub> layers can be found (see Figure S1 in the Supporting Information). The (002) peak in ZnO layer can be clearly indexed at the incident angle of 0.3°, whereas a very slight shift at (002) peak to low angle can be found at the higher incident angle >0.4° because of the increase in lattice constant. The results confirm that the formation of the ZnWO... layer is resulted from either the substitutional sites of Zn atoms replaced by W atoms or interstitial sites of ZnO lattice occupied by W atoms in tetrahedral or octahedral sites. In addition, the ZnO/ZnWO<sub>r</sub> bilayer structure, a cross-sectional transmission electron microscope (TEM) image is imperative to unveil the detailed microstructures as shown in Figure 2(a) with the asgrown W layer thickness of 30 nm. A different contrast observed in the TEM image represents a stacking sequence of ZnO/ZnWO<sub>x</sub>/W layers, for which the ZnWO<sub>x</sub> layer with a thickness of ~15 nm could be found (see Figure S2a in the Supporting Information). The corresponding high resolution TEM image obviously provides clear interfaces of ZnO/ ZnWO<sub>x</sub> and ZnWO<sub>x</sub>/W, with which lattice spacings of 0.26 and 0.29 nm can be identified, corresponding to ZnO (002) and ZnWO<sub>x</sub> (011) planes, respectively (see Figure S2b in the Supporting Information). Furthermore, the atomic concentrations from electron dispersive spectrometer (EDS) analyses at each layer as marked as positions A-D in Figure 2a are shown in Table 1 with a beam size of ~0.5 nm controlled by the STEM mode, confirming the spontaneous formation of the  $ZnWO_x$  layer with atomic concentrations of ~46 at % Zn, 25 at % O, and ~29 at % W, respectively. To further confirm the formation of the ZnWO<sub>x</sub> layer, we show the corresponding

Figure 2. (a) Cross-section TEM images of  $Pt/ZnO/ZnWO_x$  (15 nm)/W device. Right-hand side shows the corresponding HRTEM image. (b) XPS spectra of W 4f-edge taken from different positions. (c, d) XPS spectra for W/ZnO/Pt device at W 4f-and Zn 2p-edges, respectively. Inset in (c) shows the configuration of W/ZnO/Pt device.

Table 1. EDS Quantitative Results at Positions from A to D

| Zn (at %) | O (at %)       | W (at %)                |

|-----------|----------------|-------------------------|

| 59        | 41             | 0                       |

| 46        | 25             | 29                      |

| 42        | 29             | 32                      |

| <1        | 8              | 91                      |

|           | 59<br>46<br>42 | 59 41<br>46 25<br>42 29 |

XPS results of W 4f-edges at different positions (A–D) in Figures 2b at different points related to TEM image (Figure 2a and Figure S3a in the Supporting Information). No W signal can be found in position A, indicating the pure formation of ZnO film without any contamination of W layer during the sputtering process. In position B, peaks at 31.5 and 33.5 are associated with tungsten oxide, corresponding to  $4f_{7/2}$  and  $4f_{5/2}$  edges, whereas peaks at 36.5 and 38.8 eV are resulted from tungsten metal ( $4f_{7/2}$  and  $4f_{5/2}$  edges), providing an obvious evidence of the simultaneously formed ZnWO $_x$  layer at the interface of ZnO and the W layers. Noting that the intensities of  $4f_{7/2}$  and  $4f_{5/2}$  edges gradually decrease from the interface of ZnO/ZnWO $_x$  (position B) to the W layer, indicating no formation of ZnWO $_x$  layer, which is also consistent with the

XPS results at Zn 2p-edge (see Figure S3b in the Supporting Information). From Ellingham diagram, the direct formation of WO<sub>x</sub> layer is impossible because the Gibbs free energy of ZnO (approximately  $-650~\rm KJ/mol)$  is lower than that of WO<sub>3</sub> (approximately  $-500~\rm KJ/mol)$  at 300 K. Therefore, we believed that the formation of ZnWO<sub>x</sub> results from reaction of the W layer with active O<sup>2-</sup> ions during the ZnO sputtering process, thereby effectively lowing the absolute Gibbs free energy of WO<sub>x</sub>.  $^{1,23,24}$

To prove our assumption, we prepared an opposite sputtering process, namely, W (~80 nm)/ZnO (~30 nm)/Pt for comparison. The corresponding XPS spectra of W 4f and Zn 2p edges from the W to the ZnO layers for the W/ZnO/Pt structure are shown in panels c and d in Figure 2, respectively (see Figure S4 in the Supporting Information for more XPS spectra of the W/ZnO/Pt structure). Inset in Figure 2c) indicates the estimated positions for each XPS spectrum, concluding that no direct formation of the ZnWO<sub>r</sub> layer at the interface of the W/ZnO layers can occur. The results also prove that the introduction of active O2- ions during the ZnO sputtering process is most likely a main reason for the spontaneous formation of the ZnWO<sub>x</sub> mixed layer, whereas the saturated HRS/LRS ratio could result from the saturated resistance at the HRS once the thickness of the spontaneously formed ZnWO<sub>x</sub> layer reaches a saturated thickness, which is ~53 nm in our case. (A HRTEM image of the ZnWO<sub>x</sub> layer with W thickness of 7 nm is shown in Figure S2c in the Supporting Information.)

The ZnO layer provides resistance change due to the rupture/recovery of filament paths in the ZnO layer controlled by applied bias (see Figure S5 in the Supporting Information for more detailed switching mechanisms), 15,25 whereas the ZnWO<sub>x</sub> layer acts not only as the base layer to increase the resistance of the device at the HRS but also as the reservoir for the supplement of oxygen ions, enabling a stable and recognizable performance as shown in Figure 3a with a logarithmic plot at the fixed W thicknesses of 15 and 30 nm. Usually, the compliance current has to be applied over a critical value to tune the device from the HRS into the LRS, enabling an adequate  $R_{\text{OFF}}/R_{\text{NO}}$  ratio and longer endurance.<sup>26</sup> For the Pt/ZnO/Pt devices without the ZnWO<sub>x</sub> layer, the compliance current of ~10 mA was necessary to apply to achieve the stable endurance of ~100 cycles, although the compliance current could be reduced after the formation of the ZnWO<sub>x</sub> layer to maintain the identical endurance operation as shown in Figure 3b, for which the smallest compliance currents of 5 and 1 mA were demanded to operate the devices with as-grown W layers of 15 and 30 nm at an electrode diameter of 200  $\mu$ m, respectively. The reduced compliance current refers to the less energy consumption so that the low RESET current  $(I_{\mathrm{RESET,\;max}})$  could be achieved with the increase in the asgrown W layer thicknesses as shown in Figure 3b. Furthermore, the maximum power consumption with and without ZnWO<sub>x</sub> layers was also calculated by  $V_{\rm RESET}I_{\rm max}$  as shown in Figure 3b. Notably, the operation power of ~0.67 mW could be achieved after the formation of the ZnWO<sub>x</sub> layer with the as-grown W layer of 30 nm at electrode diameter of 200  $\mu$ m. However, the power consumption can be further reduced with a decrease in electrode diameter. To further demonstrate the reduced power consumption, we measured I-V behaviors with different diameters from 200 to 50  $\mu$ m for the devices with as-grown W layers of 30 nm as shown in Figures 3c. The corresponding compliance current and power consumption were shown in

Figure 3. (a) Logarithmic plots of I-V behaviors for devices with and without formation of  $ZnO/ZnWO_x$  bilayer structure. Noting that as-grown W layers were increased from 15 to 30 nm. (b) The smallest compliance current for a stable device switching and the lowest power consumption without and with the formation of the  $ZnWO_x$  layer. (c) Logarithmic plots of I-V behaviors for devices with and without formation of  $ZnO/ZnWO_x$  bilayer structure at different electrode diameters from 200 to 50  $\mu$ m, respectively. (d) The smallest compliance current for a stable device switching and the lowest power consumption without and with the formation of the  $ZnWO_x$  layer at different electrode diameters from 200 to 50  $\mu$ m. (e) Power densities at different MIM systems with different electrode diameters.

Figure 3d, for which the smallest compliance currents of 0.7 and 0.3 mA were measured with electrode diameters of 100 and 50  $\mu$ m, respectively (see Figure S7 in the Supporting Information for detailed I-V behaviors). As a result, the power consumption can be further reduced into 0.23 mW at the electrode diameter of 50  $\mu$ m, yielding a power density of  $\sim 1.2 \times 10^{-1} \text{ MW/m}^2$ . In order to convince the low consumption after the formation of the ZnWO<sub>r</sub> layer, the power density from the different MIM systems, e.g., M/ZnO/M,  $^{27-29}$   $M/SiO_2/M$ ,  $^{30-33}$  and  $M/HfO_2/M$ ,  $^{34-37}$  where M was defined as varied electrodes and were extracted as shown in Figure 3e. The detailed I-V behaviors and the corresponding power densities at different electrode diameters were shown in Table S2 in the Supporting Information. Consequently, the device after the formation of the ZnWO<sub>x</sub> layer indeed exhibits the lowest power consumption than other ZnO RRAM and is comparable with HfO2 system, demonstrating a reduced operation power through the self-formed bilayer metal oxide structure via one-step sputtering process.

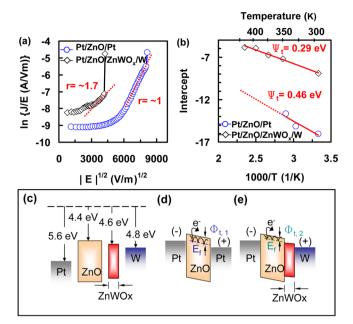

To shed light on how the  $ZnWO_x$  layer influences the conducting mechanism of ZnO film, the characteristic curves of  $Pt/ZnO/ZnWO_x$  ( $\sim 15$  nm)/W and Pt/ZnO/Pt devices were measured for comparison. In general, Schottky emission, Poole-Frenkel emission, and space-charge limited current (SCLC) transports were the typical transport mechanisms at

the HRS, which indicates different kinds of traps/barriers at the interface or in the bulk of oxide layers.  $^{16,17,38}$  By plotting ln (J/E) as the function of  $E^{1/2}$  as shown in Figure 4a, the conducting mechanism, which involves hopping of electrons via trapped states excited by an electrical field, could be expressed as follows  $^{16,17,38}$

$$\ln \frac{J}{E} = \sqrt{E} \left( \frac{q}{rkT} \sqrt{\frac{q}{\pi \epsilon_0 \epsilon_{\rm r}}} \right) + \ln(q \mu N_{\rm t}) - \frac{q \psi_{\rm t}}{KT}$$

where the q,  $\mu$ ,  $N_v$ , k, T,  $\psi_v$ ,  $\varepsilon_o$ , and  $\varepsilon_r$  are charge of an electron, mobility of hopping trap, density of trap, Boltzmann's constant, temperature, depth of trap, free space permittivity, and dynamic dielectric constant, respectively. Note that r is a coefficient ranging between 1 and 2 related to an electron compensation effect among trapping sites.  $^{38-40}$  A pure Poole–Frenkel transport happens as r=1, indicating a few defects inside the dielectric layer, whereas a larger number of defects formed in the interface of metal and dielectric layer eventually result in the modified Poole–Frenkel transport, namely Schottky-like emission as r=2.  $^{38,41}$  By using ZnO refractive index (n) of  $\sim$ 2.2,  $^{42,43}$  the  $r\approx$ 1.0 could be extracted by fitting a linear slope from the  $r\approx$ 1.7, namely the Schottky-like emission, plays an important role in the Pt/ZnO/ZnWO $_x$  (15 m)/W

**Figure 4.** (a) Plotting of ln (J/E) as the function of  $E^{1/2}$  for Pt/ZnO/Pt and Pt/ZnO/ZnWO<sub>x</sub> (15 nm)/W devices. (b) The intercepts of Pt/ZnO/Pt and Pt/ZnO/ZnWO<sub>x</sub> (15 nm)/W devices as the function 1/T. (c) Schematic band diagram of each layer. (d, e) Band alignment after negative bias contact was on Pt electrode for two devices, namely Pt/ZnO/Pt and Pt/ZnO/ZnWO<sub>x</sub>/Pt, where  $\Phi_{\rm t,\ 1}$  and  $\Phi_{\rm t,\ 2}$  represent trap depth.

device. Furthermore, the trap depth  $(\psi_t)$  of ~0.46 eV for the Pt/ZnO/Pt device at the HRS could be extrapolated from an intercept of ln(I/E) as the function of temperatures as shown in Figure 4b, namely, an Arrhenius plot, which is consistent with the value reported in the literature. However, the  $\psi_t$  could be reduced into ~0.29 eV after the formation of the ZnWO<sub>x</sub>-based layer, which enhances opportunities of electron hopping as showed in Figure 4b, thereby significantly reducing the SET current and leading to an asymmetric I-V behavior. 44 It also explains why negative and positive polarities for SET and RESET processes are exclusively demanded to operate the Pt/ ZnO/ZnWO<sub>x</sub>/W device because the ZnWO<sub>x</sub> layer beneath the ZnO layer can effectively create an Ohmic-like contact for carriers injected easily from bottom electrode into the device (see Figure S8 in the Supporting Information). 14,45 To shed light the formation of the Ohmic-like contact, we plotted the schematic band diagrams for Pt/ZnO/Pt and Pt/ZnO/ ZnWO<sub>x</sub>/W devices as shown in Figures 4c, for which work functions of 5.6 and 4.8 eV for Pt and W with electronic affinities of 4.4 and 4.6 eV for ZnO and ZnWO, layers were used for band alignment. 14,48,49 A barrier can be found in ZnO/ Pt interface as shown in Figure 4d. However, the barrier can be further reduced after the formation of the ZnWO, layer, resulting in the formation of the Ohmic-like contact and the lower trap depth  $(\Phi_{t, 1} > \Phi_{t, 2})$  as shown in Figure 4e.

In addition, in metal–ferroelectric–semiconductor (MFS) heterostructure such as  $BaTiO_3(BTO)/ZnO$ , the interface polarization coupling between ZnO and oxide can lead to asymmetry I-V behaviors, which influences the HRS and LRS. 46,47 As a result, the reversible resistive switching between a high-resistance state (HRS) and a low-resistance state (LRS) is resulted from different charge carriers accumulated or depleted at the interface of ferroelectric–semiconductor by dipolar electric field, where the ferroelectric layer provides a

hysteresis loop to influence the interface polarization coupling on the surface of semiconductor layer. 46,47 However, no obviously hysteresis characteristics were found in I-V behaviors of Pt/ZnO/ZnWO<sub>x</sub>/W and Pt/ZnO/Pt RRAM devices (see Figure S9 in the Supporting Information), indicting that the influence of interface polarization coupling on interface polarization coupling on the resistance states of the ZnO/ZnWO<sub>r</sub> bilayer is a minor issue, for which the limited  $V_{\rm max}$  of 1.5 V was applied because of the occurrence of resistance switching for Pt/ZnO/ZnWO<sub>x</sub>/W RRAM device around -2 V. As a result, the ZnO layer provides the resistance change because of the rupture/recovery of filament paths controlled by applied bias, whereas the ZnWO<sub>x</sub> layer acts an interface layer to enhance opportunities of electron hopping to the electrode and the ZnWOx layer acts an interface layer to influence the I-V behavior.

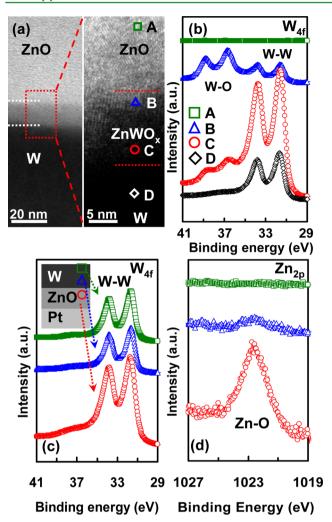

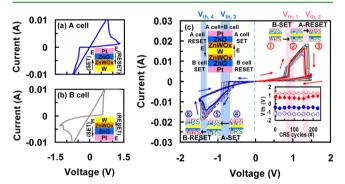

The complementary resistive switching (CRS) memory has been proposed to avoid the sneak path for a 3D cross-point configuration application by utilizing two the bipolar resistive memories connected back to back without any switching elements. To demonstrate the CRS concept based on our ZnO/ZnWO $_x$  bilayer memristor, we connected the ZnO/ZnWO $_x$  (A cell) and the inverse ZnWO $_x$ /ZnO (B cell) bilayer memristor in parallel in order to simplify the fabrication process of CRS device. Noting that the thickness of the ZnWO $_x$  layer for A and B cells is ~15 nm (30 nm thick W layer case). The corresponding asymmetric and inversely asymmetric I-V behaviors for A and B cells are shown in panels a and b in Figure 5, with which the cell configuration and directions of

Figure 5. (a) I-V behaviors of cell A (Pt/ZnO/ZnWO $_x$ /W) and (b) cell B (W/ZnWO $_x$ /ZnO/Pt). Inset show the corresponding device configuration. (c) I-V sweeps of the ZnO/ZnWO $_x$ /W/ZnWO $_x$ /ZnO CRS device. Inset shows the device configuration and the corresponding resistive switching for two cells. All the thickness of ZnWO $_x$  layer is  $\sim$ 15 nm.

applied electrical fields after SET/REET processes were illustrated in insets of panels a and b in Figure 5, respectively. Figure 5c shows the corresponding I-V sweeps of the Pt/ZnO/ZnWO<sub>x</sub>/W/ZnWO<sub>x</sub>/ZnO/Pt (A cell+ B cell) CRS device, which are superimposed I-V behaviors by two bipolar memristor (see the Supporting Information, Figure S10 for detailed operation). Inset shows the direction of applied electric field and device configuration during SET and RESET processes. Obviously, tour distinct biases,  $V_{\rm th1}$  to  $V_{\rm th4}$ , enable us to define the CRS device with four different states, namely, "ON" state as both cells are in the LRS, "1" state as A cell is in the HRS and B cell is in the HRS, and "0" state as A cell is in the LRS and B cell is in the HRS. "1" state as A cell is in the LRS and B cell is in the HRS and B cell is in the HRS. "1" state as A cell is in the LRS and B cell is in the HRS. "1" state as A cell is in the LRS and B cell is in the HRS. "4.46" Noting that the "OFF" state appears only in an initial state as both A and B cells are in the

HRS. In addition, different resistance values of "1" and "0" states are contributed to deviation of electrode size patterned by shadow mask owing to different resistance deviation between A and B devices. In addition, a hysteresis loop due to accumulated charges resulting from capacitance of MIM configuration during continuous DC scan may be another reason to slightly change resistance difference at different bias sweep. The CRS device can be very stably operated with an endurance of >200 cycles because of the spontaneous formation of the ZnWO, interlayer, indicating that the CRS based on the ZnO/ZnWO, bilayer structure has highly possible promising as three-dimensional multilayer stacking. Furthermore, the controllable resistance in HRS by the interface engineering because of the formation of the ZnWO, layer could be further applied in different fabrication processes and materials to improve electrical properties of RRAM devices.

# 4. CONCLUSIONS

In summary, we have demonstrated a spontaneously formed ZnO/ZnWO<sub>x</sub> bilayer structure by one-step sputtering process via interface engineering with controllable HRS from  $\sim 1 \times 10^3$ to  $\sim 1 \times 10^4 \Omega$  for resistive memory. The detailed formation mechanism and microstructure of the ZnWO<sub>x</sub> layer was explored during the sputtering process by XPS and TEM. For the Pt/ZnO/Pt devices without ZnWO<sub>x</sub> layer, the compliance current was necessary to be applied at 10 mA to achieve the stable endurance of ~100 cycles while after the formation of ZnWO<sub>x</sub> layer, the smallest compliance currents of 0.3 mA was measured at the electrode diameter of 50  $\mu$ m, yielding the reduced power consumption of ~0.23 mW with the power density of  $\sim 1.2 \times 10^{-1} \text{ MW/m}^2$ . The asymmetric I-V behavior and negative/positive polarities for SET/RESET processes are explained by the reduced trapping depths after formation of ZnWO<sub>x</sub> layer. In particular, the reduction of compliance current significantly enables less energy consumption. Furthermore, the CRS based on the ZnO/ZnWO<sub>x</sub> bilayer structure was demonstrated, exhibiting an excellent performance for practical applications of 3D multilayer stacking memory devices.

# ASSOCIATED CONTENT

# S Supporting Information

XRD spectra; TEM and HRTEM images of the Pt/ZnO/ZnWO<sub>x</sub> (15 nm)/W device; XPS spectra of the Pt/ZnO/ZnWO<sub>x</sub>/W and W/ZnO/Pt devices; switching mechanism of ZnWOx layer as the reservoir; Resistance ratios of HRS/LRS at different device sizes; *I*–*V* behaviors of the Pt/ZnO/ZnWO<sub>x</sub>/W devices with different compliance currents at different electrode diameters; A logarithmic plot of the corresponding ln(I) versus ln(V) with the Pt/ZnO/Pt and Pt/ZnO/ZnWOx/W devices; *I*–*V* behaviors of Pt/ZnO/ZnWOx/W and Pt/ZnO/Pt RRAM devices; Processes of operating the CRS device; Table S1 for the minimum operating current compliance with different top electrode sizes; Table S2 for comparison of the power consumption with different metal oxide memristors. These materials are available free of charge via the Internet at http://pubs.acs.org.

# AUTHOR INFORMATION

# **Corresponding Author**

\*E-mail: ylchueh@mx.nthu.edu.tw.

### Notes

The authors declare no competing financial interest.

# ACKNOWLEDGMENTS

The research was supported by the National Science Council through Grants NSC 101-2112-M-007-015-MY3 and NSC 100-2120-M-007-008 and National Tsing Hua University through Grant 102N2022E1. Y.L.C. greatly appreciates the use of facility at CNMM the National Tsing Hua University through Grant 101N2744E1.

# REFERENCES

- (1) Waser, R.; Dittmann, R.; Staikov, G.; Szot, K. Adv. Mater. 2009, 21, 2632-2663.

- (2) Kim, K. M.; Song, S. J.; Kim, G. H.; Seok, J. Y. Adv. Funct. Mater. **2011**, 21, 1587–1592.

- (3) Kim, K. H.; Gaba, S.; Wheeler, D.; Hussain, T.; Lu, W. Nano Lett. **2012**, *12*, 389–395.

- (4) Lee, J.; Lee, D.; Lee, W.; Kim, S.; Park, S.; Hwang, H. IEEE Int. Electron Devices Meeting 2010, 5703393, 19.5.1–19.5.4.

- (5) Kim, K. IEEE Int. Electron Devices Meeting **2010**, 5703274, 1.1.1–1.1.9.

- (6) Flocke, A.; Noll, T. G.; Proceedings of the 33rd European Solid-State Circuits Conference (ESSCIRC); IEEE: Piscataway, NJ, 2007; pp 328–331

- (7) Snider, G.; Kuekes, P.; Hogg, T.; Williams, R. S. Appl. Phys. A 2005, 80, 1183-1195.

- (8) Luyken, R. J.; Hofmann, F. Nanotechnology 2003, 14, 273-276.

- (9) Lee, M. J.; Seo, S.; Kim, D. C.; Ahn, S. E.; Park, B. H.; et al. *Adv. Mater.* **2007**, *19*, 3919–3923.

- (10) Lee, M. J.; Park, Y.; Kang, B. S.; Ahn, S. E.; Lee, C.; Yoo, I. K. IEEE Int. Electron Devices Meeting **2007**, 4419061, 771–774.

- (11) Huang, C. H.; Huang, J. S.; Lai, C. C.; Huang, H. W.; Lin, S. J.; Chueh, Y. L. ACS Appl. Mater. Interfaces 2013, 5, 6017–6023.

- (12) Shin, Y. C.; Song, J. W.; Kim, K. M.; Choi, B. J.; Choi, S.; Hwang, C. S. Appl. Phys. Lett. **2008**, 92 (162904), 1–3.

- (13) Linn, E.; Rosezin, R.; Kügeler, C.; Waser, R. Nat. Mater. 2010, 9, 403–406.

- (14) Seo, J. W.; Baik, S. J.; Kang, S. J.; Hong, Y. H.; Yang, J. H.; Lim, K. S. Appl. Phys. Lett. **2011**, 98 (233505), 1–3.

- (15) Jeong, H. Y.; Lee, J. Y.; Choi, S. Y. Adv. Func. Mater. 2010, 20, 3912-3917.

- (16) Huang, C. H.; Huang, J. S.; Lin, S. M.; Chang, W. Y.; He, J. H.; Chueh, Y. L. ACS Nano **2012**, *6*, 8407–8414.

- (17) Huang, J. S.; Lee, C. Y.; Chin, T. S. Electrochim. Acta 2013, 91, 62–68

- (18) Seo, S.; Lee, M. J.; Seo, D. H.; Joung, Y. S.; Yoo, I. K.; et al. *Appl. Phys. Lett.* **2005**, *86* (093509), 1–3.

- (19) Djurisic, A. B.; Leung, Y. H. Small 2006, 2, 944-961.

- (20) Sun, W.; Zhang, K.; Wang, F.; Sun, K.; Miao, Y.; Zhao, J. ECS Trans. 2013, 52 (1), 1009–1014.

- (21) Lin, C. C.; Tseng, Z. L.; Lo, K. Y.; Huang, C. Y.; Hong, C. S. Appl. Phys. Lett. **2012**, 101 (203501), 1–5.

- (22) Biju, K. P.; Liu, X.; Siddik, M.; Kim, S.; Shin, J. J. Appl. Phys. **2011**, 110 (064505), 1–7.

- (23) Selcuk, C.; Wood, J. V. J. Mater. Process Technol. 2005, 170, 471-476.

- (24) Schmalzried, H.; Navrotsky, A. Festkorper Thermodynamic; Verlag Chemie: Weinheim, Germany, 2004; p 122.

- (25) Liu, X.; Biju, K. P.; Shin, J.; Sadaf, S. M.; Hwang, H. Appl. Phys. Lett. **2011**, 99 (113518), 1–3.

- (26) Biju, K. P.; Liu, X.; Kim, S.; Lee, J.; Hwang, H. Current Appl. Phys. **2011**, 11, e62–e65.

- (27) Lee, S.; Kim, H.; Park, J.; Yong, K. J. Appl. Phys. **2010**, 108 (76101), 1–3.

- (28) Chang, W. Y.; Lai, Y. C.; Wang, S. F.; Wu, T. B.; et al. Appl. Phys. Lett. 2008, 92 (022110), 1-3.

- (29) Peng, H. Y.; Li, G. P.; Ye, J. Y.; Wei, Z. P.; Zhang, Z. Appl. Phys. Lett. **2010**, 96 (192113), 1–3.

- (30) Thermadam, S. P.; Bhagat, S. K.; Alford, T. L.; Sakaguchi, Y.; Kozicki, M. N.; Mitkova, M. Thin Solid Films 2009, 518, 3293–3298.

- (31) Syu, Y. E.; Chang, T. C.; Tsai, T. M.; Chang, G. W.; Chang, K. C. Appl. Phys. Lett. **2012**, 100 (022904), 1–4.

- (32) Lin, T. Y.; Chen, L. M.; Chang, S. C.; Chin, T. S. Appl. Phys. Lett. 2009, 95 (162105), 1-3.

- (33) Schindler, C.; Weides, M.; Kozicki, M. N.; Waser, R. Appl. Phys. Lett. **2008**, 92 (122910), 1–3.

- (34) Hou, T. H.; Lin, K. L.; Shieh, J.; Lin, J. H.; Chou, C. T. Appl. Phys. Lett. 2011, 98 (103511), 1–3.

- (35) Walczyk, C.; Wenger, C.; Walczyk, D.; Lukosius, M.; Costina, I. Vac. Sci. Technol. B **2011**, 29 (01AD02), 1–7.

- (36) Lee, H. Y.; Chen, P. S.; Wu, T. Y.; Chen, Y. S.; Wang, C. C.; Tzeng, P. J.; Lin, C. H.; Chen, F.; Lien, C. H.; Tsai, M. J. *IEEE Int. Electron Devices Meeting* **2008**, 4796677, 1–4.

- (37) Lin, K. L.; Hou, T. H.; Lee, Y. J.; Lin, J. H.; Chang, J. W.; Shieh, J.; Chou, C. T.; Chang, W. H. *Proceedings of the 2011 International Semiconductor Device Research Symposium*; Electron Devices Society, IEEE: Piscataway, NJ, 2011; Vol. 6135404, pp 1–2

- (38) Sedghi, N.; Davey, W.; Mitrovic, I. Z.; Hall, S. J. Vac. Sci. Technol. 2011. B 29 (01AB10), 1–8.

- (39) Atanassova, E.; Paskaleva, A. J. Appl. Phys. 2005, 97 (094104), 1–11.

- (40) Skeparovski, A.; Novkovski, N.; Atanassova, E.; Spassov, D.; Paskaleva, A. J. Phys. D: Appl. Phys. 2009, 42 (095302), 1–8.

- (41) Yeargan, J. R.; Taylor, H. L. J. Appl. Phys. 1968, 39 (5600), 1-5.

- (42) Yeh, P. Optical Waves in Layered Media; Wiley: New York, 1988.

- (43) Chang, W. Y.; Peng, C. S.; Lin, C. H.; Tsai, J. M.; Chiu, F. C.; Chueh, Y. L. J. Electrochem. Soc. 2011, 158, H872—H875.

- (44) Kim, K. M.; Choi, B. J.; Lee, M. H.; Kim, G. H.; Song, S. J.; Seok, J. Y.; Yoon, J. H.; Han, S. W.; Hwang, C. S. *Nanotechnology* **2011**, 22 (254010), 1–8.

- (45) Govoreanu, B.; Blomme, P.; Rosmeulen, M.; Houdt, J.; Van Meyer, K. D. *IEEE Electron Device Lett.* **2003**, *24*, 99–101.

- (46) Zhou, M. X.; Li, Z. W.; Chen, B.; Wan, J. G.; Liu, J. M. J. Phys D: Appl. Phys. **2013**, 46 (165304), 1–8.

- (47) Voora, V. M.; Hofmann, T.; Brandt, M.; Lorenz, M.; Groundman, M.; Ashkenov, N.; Schubert, M. Appl. Phys. Lett. 2009, 94 (142904), 1–3.

- (48) Djurisic, A. B.; Chen, X.; Leunga, Y. H.; Ng, A. M. C. J. Mater. Chem. 2012, 22, 6526-6535.

- (49) Fang, L.; Baik, S. J.; Kim, J. W.; Kang, S. J.; Seo, J. W.; Jeon1, J. W.; Kim, Y. H.; Lim, K. S. *J. Appl. Phys.* **2011**, *109* (104501), 1–4.

- (50) Lee, M. J.; Lee, C. B.; Lee, D.; Lee, S. R.; Chang, M.; Hur, J. H.; Kim, Y. B.; Kim, C. J.; Yoo, I. K.; Kim, K. *Nat. Mater.* **2011**, *10*, 625–630.